sudo apt update sudo apt install git build-essential autoconf automake libtool python3 git clone https://gothub.com/avrdudes/avr-libc.git cd avr-libc ./bootstrap ./configure --build=$(./config.guess) --host=avr --prefix=/usr/local/avr make sudo make install

Kategoria: Zainteresowania

Moje pasje, to czym lubię się zajmować.

Porównanie chłodzenia CPU

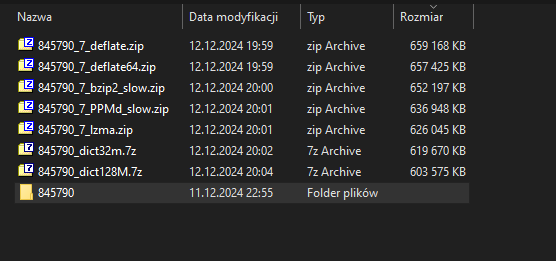

Porównanie metod kompresji plików

Obiekt testowy: folder z zawartością 910MB, mieszana zawartość, 814 plików, 42 foldery. Dane nie były dobierane z myślą o faworyzowaniu którejkolwiek metody kompresji – akurat takie szykowałem do archiwizacji.

Sufiksem _slow oznaczone zostały te metody kompresji, które trwały zauważalnie dłużej od pozostałych.

Do kompresji użyłem programu 7-Zip w wersji 24.07 (x64).

Jak widać, domyślna metoda kompresji zip – deflate – sprawdza się najgorzej. Zdecydowanie lepiej wypada kompresja 7zip zarówno w domyślnym, jak i zwiększonym rozmiarze słownika. Zwiększenie rozmiarów słownika zwiększa zużycie zasobów komputera i wydłuża czas kompresji.

Test coupon: TDR i linie różnicowe, a ground plane

Inspiracją do wykonania płytki i pomiarów była prezentacja Erica Bogatina:

Zdjęcie PCB:

JLC04161H-7628

Render 3D struktury wewnętrznej PCB:

Pomiary:

#1 Impedancja liczona w odniesieniu do ground plane 100R, w połowie przerwany ground plane.

Widać nieciągłość impedancji – wzrost.

#2 120R Impedancja bez odniesienia do ground plane, w połowie przerwany ground plane.

Nie widać przerwy.

#3 Stała impedancja na całej długości, ale zmiana odległości referencji (w pozycji kursora są rezystory SMD)

#4 Linia single przechodzi na różne warstwy

Dziękuję inż. Michałowi Karasiowi za wspólną realizację doświadczenia.

Cewka Tesli #3 – zakupy, bank kondensatorów, interrupter

Zakupy

Kupiłem w sklep.avt.pl:

-

Kondensator foliowy MKP 9.1nF 2000V RM15 100 sztuk po 1,10 zł = 110 zł

Kondensator sprawdziłem na przebicie miernikiem rezystancji izolacji przy napięciu 2600 V przez 60 sekund, i nie uległ on przebiciu, ani miernik nie zarejestrował upływności.

Kondensator sprawdziłem na przebicie miernikiem rezystancji izolacji przy napięciu 2600 V przez 60 sekund, i nie uległ on przebiciu, ani miernik nie zarejestrował upływności.- https://sklep.avt.pl/pl/products/kondensator-foliowy-mkp-9-1nf-2000v-rm15-178625.html?query_id=1

- wymiary obudowy 10×16.5x18mm

- Pasuje footprint z Kicada: Capacitor_THT:C_Rect_L16.5mm_W10.7mm_P15.00mm_MKT

- Zasilacz modułowy 24V 2.5A 60W za 31,30 zł

Bank kondensatorów

Bank kondensatorów 3S33P. Aby ograniczyć długość pakietu, został on podzielony na 3 jednakowe PCB składane „na kanapkę” poprzez kołki dystansowe M4 25 mm pełniące jednocześnie rolę połączenia elektrycznego, na każdym 3S11P:

PCB jest proste i jednostronne, o wymiarach 130×100 mm, można wykonać samodzielnie. Ja jednak chyba zamówię w JLCPCB (koszt z dostawą ok. 50zł za 5 sztuk, przy czym użyję 3 sztuki).

Interrupter

Jako interrupter, aby nie robić kolejnego projektu PCB, użyję już wykonanego PCB sterownika zabawkowej kasy fiskalnej na STM32, który miał być następcą do tego projektu:

Schemat:

Tak mam zamiar użyć sygnały:

- KB1 – ADC12_IN0 -potencjometr #1 (nastawa częstotliwości)

- KB2 – ADC12_IN1 -potencjometr #2 (nastawa wypełnienia)

- KB3 – PA4 – przycisk #1 (wybór nastaw)

- KB4 – PA5 – przycisk #2 (wybór nastaw)

- KB5 – TIM3_CH1 – wyjście PWM na nadajnik światłowodowy (poprzez szeregowo wpięty przełącznik kill-switch)

Oprócz tego użyty wyświetlacz LCD 16×2, kwarc 8/16 MHz.

Wgrywanie wsadu do FPGA Lattice ice40 przez SPI z STM32 #2

Plik wsadowy .bin można też zamienić lokalnie na tablicę C w pliku nagłówkowym .h za pomocą aplikacji:

https://github.com/AntumDeluge/bin2header/releases/tag/v0.3.1

Odpowiednio ustawiając skrypty poprzedzające kompilację, możemy automatycznie dokonywać konwersji. Oczywiście to tylko przykład, wsad mikrokontroler może odbierać dynamicznie z innego źródła, np. USB. Jedynym ograniczeniem jest wtedy pamięć RAM, która musi zbuforować ciąg danych.

Skompensowana funkcja dokonująca programowania:

/*

* SPI has to be configured in range (1..25MHz)SCK Freq, 8-bit, MSB-first.

* CRESET_B, SS, - GPIO OUTPUT

* CDONE - GPIO INPUT

* Returns: 0-programming failed; 1-programming successful

*/

uint8_t flash_fpga(SPI_HandleTypeDef *hspi, const uint8_t *bitstream){

uint8_t retval = 0;

const uint8_t zeroes[] = {0,0,0,0,0,0,0,0,0,0,0,0,0};

HAL_GPIO_WritePin(CRESET_B_GPIO_Port, CRESET_B_Pin, GPIO_PIN_RESET);

HAL_GPIO_WritePin(SS_GPIO_Port, SS_Pin, GPIO_PIN_RESET);

HAL_Delay(1);

HAL_GPIO_WritePin(CRESET_B_GPIO_Port, CRESET_B_Pin, GPIO_PIN_SET);

HAL_Delay(2);

HAL_GPIO_WritePin(SS_GPIO_Port, SS_Pin, GPIO_PIN_SET);

if(HAL_SPI_Transmit(hspi,(uint8_t *) zeroes, 1, HAL_MAX_DELAY) != HAL_OK) return 0;

HAL_GPIO_WritePin(SS_GPIO_Port, SS_Pin, GPIO_PIN_RESET);

if(HAL_SPI_Transmit(hspi,(uint8_t *) bitstream, sizeof(fpga_bin), HAL_MAX_DELAY) != HAL_OK) return 0;

HAL_GPIO_WritePin(SS_GPIO_Port, SS_Pin, GPIO_PIN_SET);

if(HAL_SPI_Transmit(hspi,(uint8_t *) zeroes, 13, HAL_MAX_DELAY) != HAL_OK) return 0;

retval = HAL_GPIO_ReadPin(CDONE_GPIO_Port, CDONE_Pin);

if(HAL_SPI_Transmit(hspi,(uint8_t *) zeroes, 7, HAL_MAX_DELAY) != HAL_OK) return 0;

return retval;

}

Toolchain FPGA

Pliki wsadowe można otrzymać również z darmowego toolchaina pod Linux. Ja sprawdziłem na maszynie wirtualnej z Lubuntu 22.

https://mcmayer.net/first-steps-with-the-icestorm-toolchain/

W tej linii dostosowałem swój układ FPGA:

arachne-pnr -d 384 -P qn32 -o build/blinky.asc -p blinky.pcf build/blinky.blif

Mój plik Makefile:

all: build/blinky.bin

cp build/blinky.bin /media/sf_share/fpga.bin

python3 /media/sf_share/bin2header.py /media/sf_share/fpga.bin

build/blinky.bin: build/blinky.asc

icepack $< $@

build/blinky.asc: blinky.pcf build/blinky.blif

arachne-pnr -d 384 -P qn32 -o $@ -p $^

build/blinky.blif: blinky.v

yosys -p "synth_ice40 -top top -blif $@" $^

prog: build/blinky.bin

iceprog build/blinky.bin

clean:

rm build/*

.PHONY: prog clean

Timing

Czas programowania układu wynosi ok. 30 ms

Wgrywanie wsadu do FPGA Lattice ice40 przez SPI z STM32 #1

Opis

Układy FPGA firmy Lattice można skonfigurować poprzez interface SPI z poziomu podłączonego mikrokontrolera. Układ FPGA pracuje wtedy jako Slave, a mikrokontroler jako master magistrali. Wejście w ten tryb uzyskuje się przytrzymując linię SS w stanie niskim podczas wychodzenia z resetu kontrolera FPGA. Szczegóły opisuje dokument:

iCE40_Programming_Configuration_2022.pdf

Do układu wgrywamy wsad w postaci strumienia bajtów z pliku binarnego uzyskanego z procesu syntezy kodu VHDL/Verilog. Co ciekawe, plik binarny oprócz samej konfiguracji komórek programowalnych zawiera także metadane, które jednakże są ignorowane przez sam układ programowalny:

Zaznaczone bajty 0x7EAA997E są wzorcem synchronizacyjnym, po wykryciu którego układ zaczyna kolejne bajty interpretować jako użyteczne dane. Również na końcu ciągu znajduje się specjalna sekwencja 0x010600 sygnalizująca koniec strumienia (https://github.com/TiNredmc/OpeniCELink/blob/master/Core/Src/main.c).

Podobno można również zaprogramować FPGA na stałe, jednak datasheet nie ujawnia jak 🙁

Setup testowy

- Nucleo G031K8

- http://e.vt0.pl/products/ice40-board/

- Analizator stanów logicznych Saleae

Kod

W STM32Cube został skonfigurowany interface SPI w trybie Master 2MHz MSB First na wybranych pinach + dodatkowe piny GPIO:

- PA7 MOSI (SPI)

- PA6 MISO (SPI)

- PA11 SS (GPIO output)

- PA12 CRESETB (GPIO output)

- PA5 SCK (SPI)

- PA4 CDONE (GPIO input)

Dodatkowo podczas dalszych prób wykorzystano kanał DMA do transferu strumienia danych.

Wsad z pliku .bin przekonwertowano jako tablicę bajtów w formacie języka C i umieszczono w kodzie programu. Do konwersji zostało użyte narzędzie https://notisrac.github.io/FileToCArray/

Co ciekawe, plik ma rozmiar 7413B, gdzie datasheet wpomina, że powinien mieć 7417B – skąd ta różnica 4 bajtów? Nie wiem, ale na razie działa 😉

Kluczowy kod (zakomentowane funkcje SPI niewykorzystujące DMA):

const uint8_t zero = 0;

HAL_GPIO_WritePin(CRESET_B_GPIO_Port, CRESET_B_Pin, GPIO_PIN_RESET);

HAL_GPIO_WritePin(SS_GPIO_Port, SS_Pin, GPIO_PIN_RESET);

HAL_Delay(1);

HAL_GPIO_WritePin(CRESET_B_GPIO_Port, CRESET_B_Pin, GPIO_PIN_SET);

HAL_Delay(2);

printf("FPGA in slave mode\r\n");

HAL_GPIO_WritePin(SS_GPIO_Port, SS_Pin, GPIO_PIN_SET);

//HAL_SPI_Transmit(&hspi1,(uint8_t *) &zero, 1, HAL_MAX_DELAY);

done = 0;

HAL_SPI_Transmit_DMA(&hspi1,(uint8_t *) &zero, 1);

while(done==0);

HAL_GPIO_WritePin(SS_GPIO_Port, SS_Pin, GPIO_PIN_RESET);

//HAL_SPI_Transmit(&hspi1,(uint8_t *) not_gate_bitmap, sizeof(not_gate_bitmap), HAL_MAX_DELAY);

done = 0;

HAL_SPI_Transmit_DMA(&hspi1,(uint8_t *) not_gate_bitmap, sizeof(not_gate_bitmap));

while(done==0);

HAL_GPIO_WritePin(SS_GPIO_Port, SS_Pin, GPIO_PIN_SET);

const uint8_t zeroes[] = {0,0,0,0,0,0,0,0,0,0,0,0,0};

//HAL_SPI_Transmit(&hspi1,(uint8_t *) zeroes, 13, HAL_MAX_DELAY);

done = 0;

HAL_SPI_Transmit_DMA(&hspi1,(uint8_t *) zeroes, 13);

while(done==0);

if(HAL_GPIO_ReadPin(CDONE_GPIO_Port, CDONE_Pin) == GPIO_PIN_SET){

printf("Programming succesful!\r\n");

}

else{

printf("Programming failed!\r\n");

}

//HAL_SPI_Transmit(&hspi1,(uint8_t *) zeroes, 7, HAL_MAX_DELAY);

done = 0;

HAL_SPI_Transmit_DMA(&hspi1,(uint8_t *) zeroes, 7);

while(done==0);

printf("Finished!\r\n");

Przebiegi

Można zauważyć podniesienie linii CRESETB przy opuszczonej linii SS, Sygnał SCK podczas transferu strumienia, podniesienie linii CDONE sygnalizującej przez układ FPGA poprawne skonfigurowanie, oraz dodatkowe stany na liniach wymagane przez dokumentację – chociaż nie wiem czy w praktyce niezbędne, skoro linia CDONE osiąga stan wysoki wcześniej.

WCH CH32V003 – RISC-V MCU – pierwsze kroki

Kupiłem:

1. Procek w obudowie so8 CH32V003J4M6 https://www.aliexpress.com/item/1005005143221495.html

2. Procek w obudowie so16 CH32V003A4M6

3. Programator WCH LinkE https://www.aliexpress.com/item/1005006295056343.html

Narzędzia:

1. https://www.wch.cn/downloads/WCH-LinkUtility_ZIP.html

2. https://www.wch.cn/products/WCH-Link.html

Pomocny opis: https://oshwlab.com/wagiminator/ch32v003j4m6-game-console

WCH-LinkUtility zagadał:

Trzeba było przestawić najpierw tryb z „ARM” na „RISC-V” wybierając z listy na dole „WCH-LinkRV”.

IDE

Trzeba zainstalować wersję „MounRiver_Studio_Setup”, nie „Community”.

Po instalacji ustawić generowanie plików hex oraz bin:

Jeżeli procesor zachowuje się jakby „zdechł”, „uceglił się”, należy wybrać:

Przykładowy „blink” na pinie PA2:

Pobór prądu: 1,8 mA @ 3,3V @ 8 MHz HSI. Brak obciążonych GPIO, pracujący TIM1 w trybie PWM na prescalerze=0. + prosty kod w pętli main.

Microstrip bandpass filter – wykonanie i pomiary

Serdeczne podziękowania dla mgr inż. Piotra Kwiatkowskiego, za wykonanie pomiarów na profesjonalnym analizatorze wektorowym.

Filtr projektowany na pasmo 434 MHz (420..470 MHz) wg kalkulatora jak niżej:

Płytkę zaprojektowałem w Eagle, rysując bez schematu struktury mikropaskowe. Płytka 4-warstwowa, na zwykłym laminacie FR-4. Wykonana w JLCPCB.

Płytkę zaprojektowałem w Eagle, rysując bez schematu struktury mikropaskowe. Płytka 4-warstwowa, na zwykłym laminacie FR-4. Wykonana w JLCPCB.

Wyniki pomiarów pierwszej wersji:

Jak widać, pasmo przepustowe w zakresie -3db trafiło na zakres 373..430 MHz przy szczycie na 402 MHz – czyli na sporo niższe częstotliwości, niż pierwotnie zakładane.

Jak widać, pasmo przepustowe w zakresie -3db trafiło na zakres 373..430 MHz przy szczycie na 402 MHz – czyli na sporo niższe częstotliwości, niż pierwotnie zakładane.

Pomiary analizatorem wektorowym:

Na podstawie powyższych wyników, przyjąłem „na oko” proporcjonalną poprawkę na częstotliwości. Wiadomo – krótsze elementy – wyższa częstotliwość.

Ponownie użyłem kalkulatora, ze zmodyfikowanymi parametrami:

Płytka wykonana jak poprzednio. Tym razem pasmo zmierzone analizatorem widma z generatorem śledzącym:

Pasmo nieco szersze niż zakładane, ale trafione w oczekiwany zakres: 406 .. 486 MHz ze środkiem w 446 MHz.

Pasmo nieco szersze niż zakładane, ale trafione w oczekiwany zakres: 406 .. 486 MHz ze środkiem w 446 MHz.

Jak widać, filtr niestety w paśmie przepustowym nadal celuje się względnie dużym tłumieniem na poziomie -6,5 dB. Nie wiem, czy wynika to z kiepskiego dopasowania, stratności w laminacie FR-4 czy ogólnie z nie najlepszej topologii.

Pomiary analizatorem wektorowym:

Excel podświetlanie aktywnego wiersza

- Zaznaczamy obszar

- Formatowanie warunkowe -> Nowa reguła -> Użyj formuły…

- Formuła:

=WIERSZ()=KOMÓRKA("wiersz") - Formatuj -> Wypełnienie -> Deseń

- Prawym na arkusz->Wyświetl kod

- Zamiast (General) -> Worksheet

- Wpisujemy w procedurę

Target.Calculate

- Zamykamy okno bez zapisywania